- 您现在的位置:买卖IC网 > Sheet目录1203 > COREFFT-RM (Microsemi SoC)IP MODULE COREFFT

�� �

�

�

�CoreFFT� Fast� Fourier� Transform�

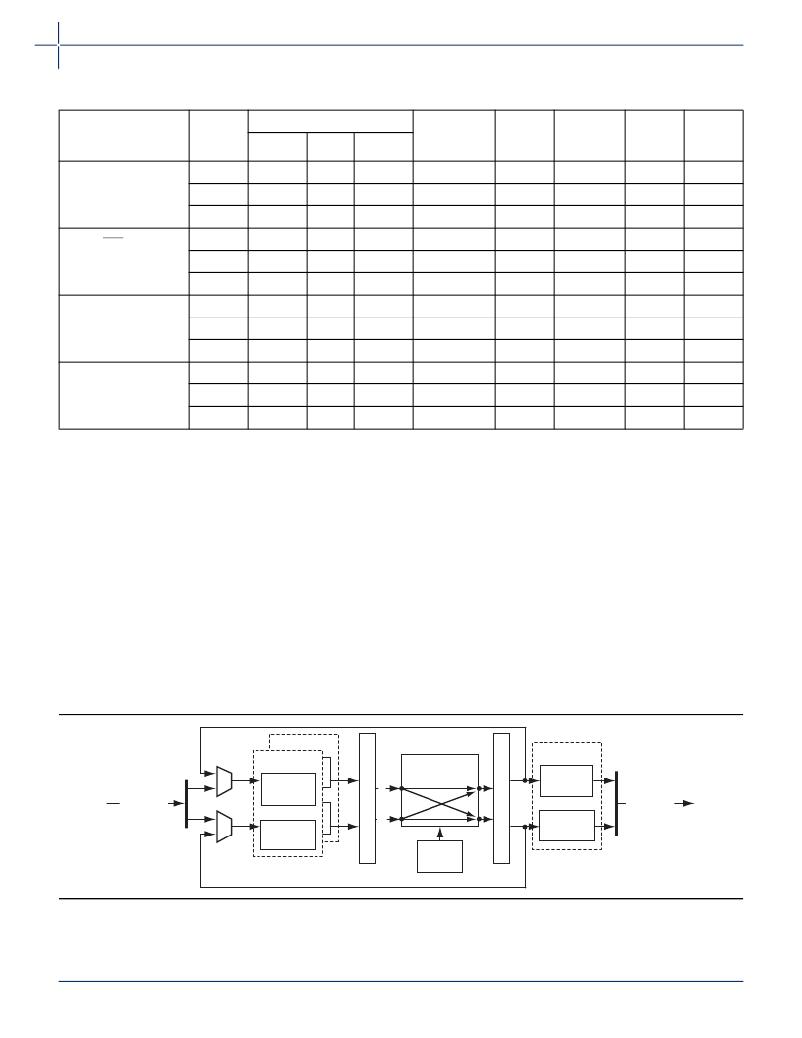

�Table� 2� ?� CoreFFT� Device� Utilization� and� Performance� (bit� width� b� =� 8)�

�Cells� or� Tiles�

�Device�

�Clock�

�FFT�

�FPGA� Family� and�

�FFT�

�Utilization�

�RAM�

�Speed�

�Rate,�

�Time,�

�Device�

�ProASIC3/E� A3P1000�

�ProASIC� PLUS� APA1000�

�Axcelerator� AX1000�

�RTAX-S� RTAX1000S�

�Points�

�256�

�512�

�1,024�

�256�

�512�

�1,024�

�256�

�512�

�1,024�

�256�

�512�

�1,024�

�Comb�

�2,126�

�2,283�

�2,509�

�2,386�

�2,569�

�2,759�

�1,317�

�1,435�

�1,620�

�1,317�

�1,435�

�1,611�

�Seq�

�968�

�989�

�1,026�

�949�

�974�

�1,124�

�958�

�986�

�1,016�

�958�

�986�

�1,027�

�Total�

�3,094�

�3,272�

�3,535�

�3,335�

�3,543�

�3,883�

�2,275�

�2,421�

�2,636�

�2,275�

�2,421�

�2,638�

�%�

�12.6%�

�13.3%�

�14.4%�

�5.9%�

�6.3%�

�6.9%�

�12.5%�

�13.3%�

�14.5%�

�12.5%�

�13.3%�

�14.5%�

�Blocks�

�7�

�7�

�14�

�14�

�14�

�28�

�7�

�7�

�14�

�7�

�7�

�14�

�Grade�

�–2�

�–2�

�–2�

�Std�

�Std�

�Std�

�–2�

�–2�

�–2�

�–1�

�–1�

�–1�

�MHz�

�114�

�122�

�118�

�87�

�82�

�82�

�170�

�159�

�137�

�132�

�116�

�101�

�μsec�

�10�

�20�

�44�

�13�

�29�

�64�

�7�

�15�

�38�

�8�

�21�

�52�

�Notes:�

�1.� Auto-scaling� (block� floating� point)� is� enabled� in� all� cases.�

�2.� The� above� data� were� obtained� by� typical� synthesis� and� place-and-route� methods.� Other� core� parameter� settings� can� result� in�

�different� utilization� and� performance� values.�

�3.� All� memory� buffers� are� RAM-block-based.�

�4.� Timing� constraints� supplied� with� CoreFFT� were� used.�

�5.� Timing-driven� layout� options� were� used,� effort� level� 3,� with� no� multiple� passes.�

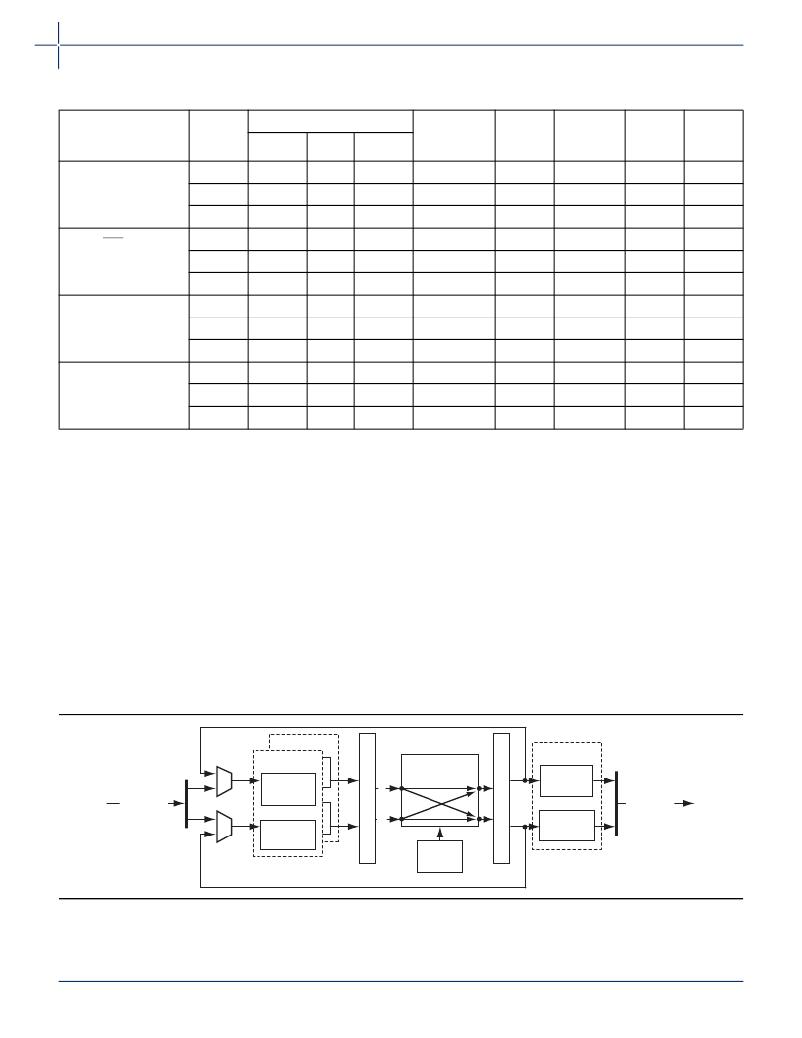

�Architecture�

�The� CoreFFT� module� input� and� output� data� are� stored� in�

�on-chip� RAM� blocks.� The� input� memory� buffer� is� also�

�used� by� the� FFT� processor� as� working� memory� where� the�

�FFT� engine� stores� results� obtained� at� any� intermediate�

�FFT� stage.� This� dual� memory� usage� is� possible� due� to� the�

�in-place� FFT� algorithm� implemented� by� the� core.�

�The� twiddle� factors� (algorithm� coefficients)� used� by� the�

�FFT� processor� are� generated� by� CoreFFT� and� stored� in� a�

�RAM-based� LUT.�

�In� addition� to� the� FFT� processor,� the� resulting� module�

�also� contains� control� logic� and� a� host� interface� used� for�

��Pong� Buffer�

�Ping� Buffer�

�Radix-2�

�Data� Buffer�

�Complex�

�Mem� 0�

�P�

�Butterfly�

�Mem� 0�

�Complex�

�Input� Data�

�FFT� Output�

�Figure� 2� ?� CoreFFT� Architecture�

�4�

�Mem� 1�

�Q�

�v4.0�

�Twiddle�

�LUT�

�Mem� 1�

�Bit-Reversed�

�Write� Addr�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREFIR-RM

IP MODULE COREFIR

COREPCIF-RM

IP MODULE COREPCIF

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

相关代理商/技术参数

COREFFT-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREFFT-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREFIR-AR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-EV

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-RM

功能描述:IP MODULE COREFIR RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384

COREFIR-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREMP7

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreMP7